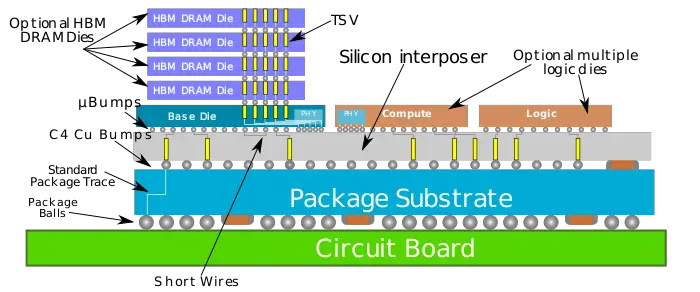

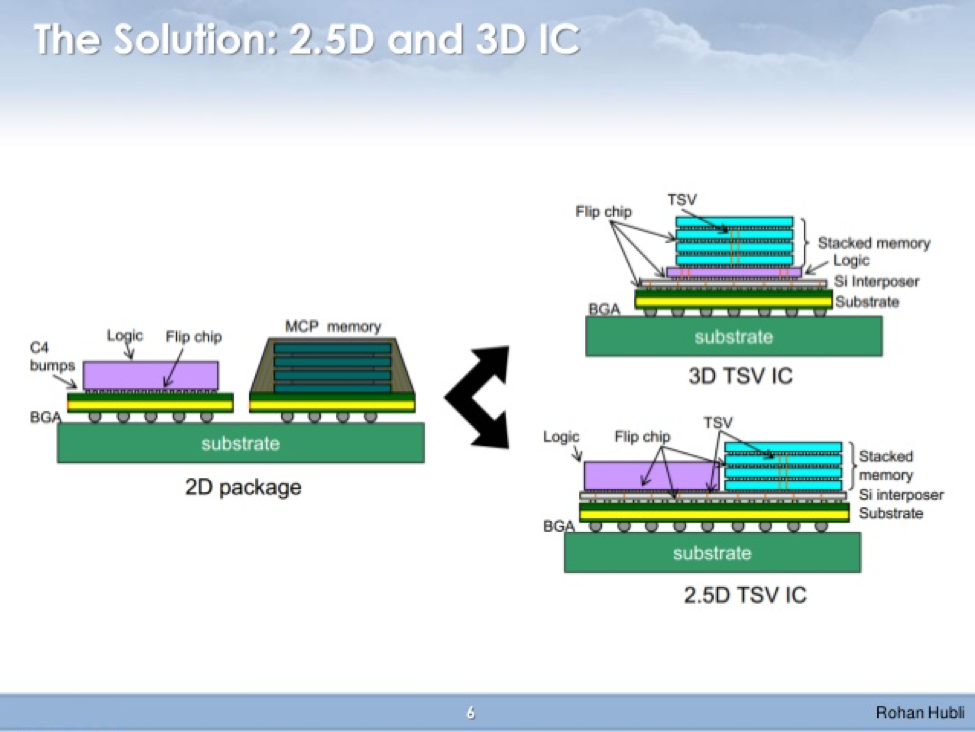

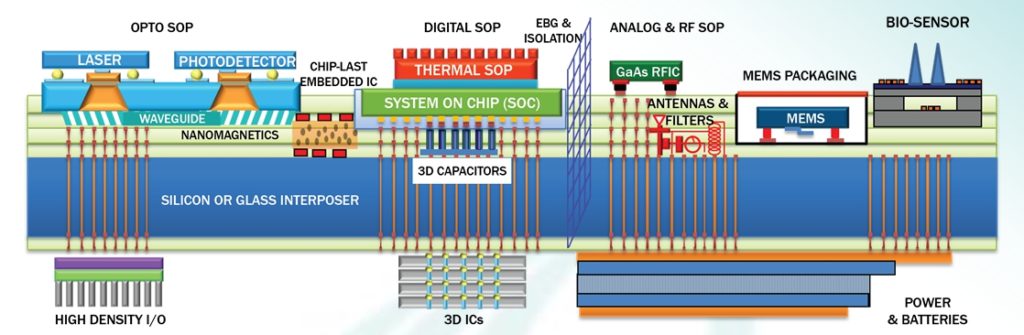

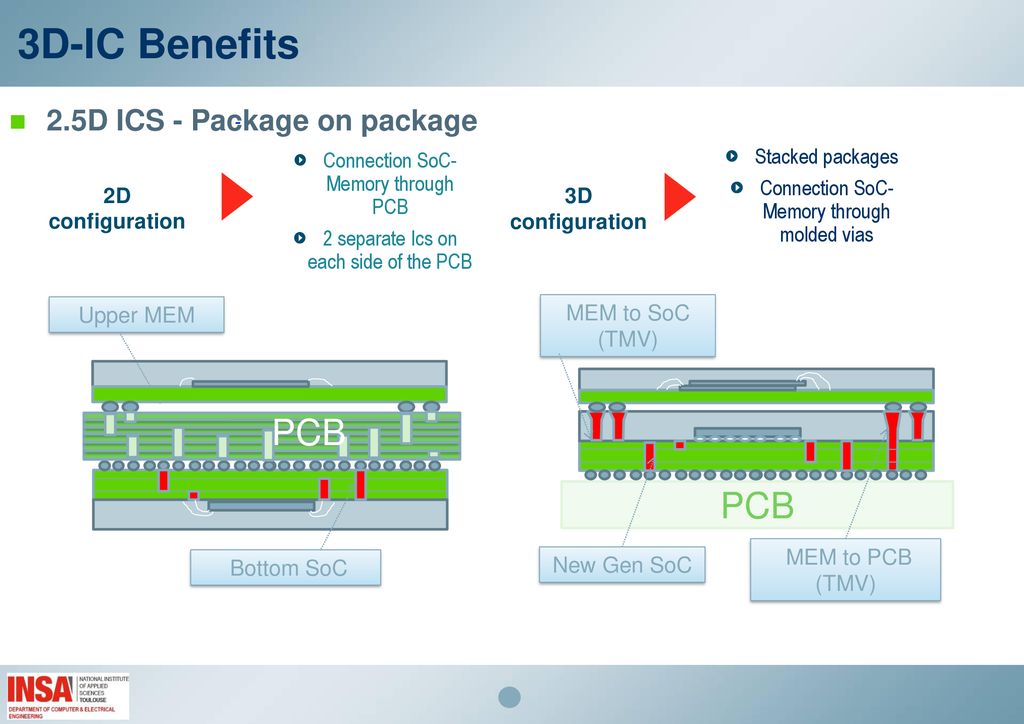

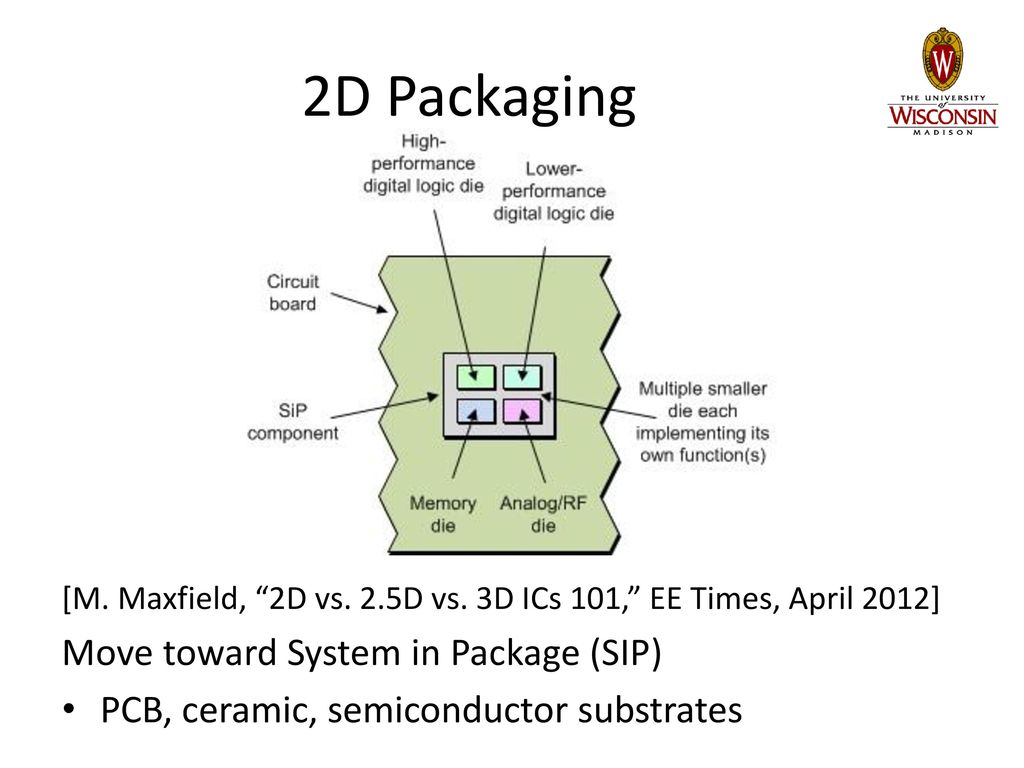

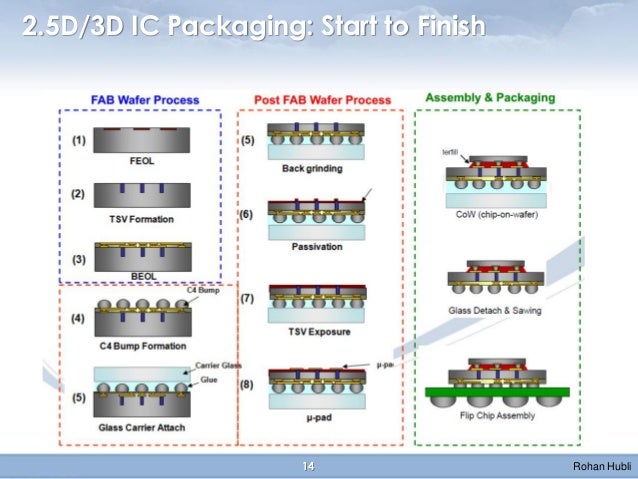

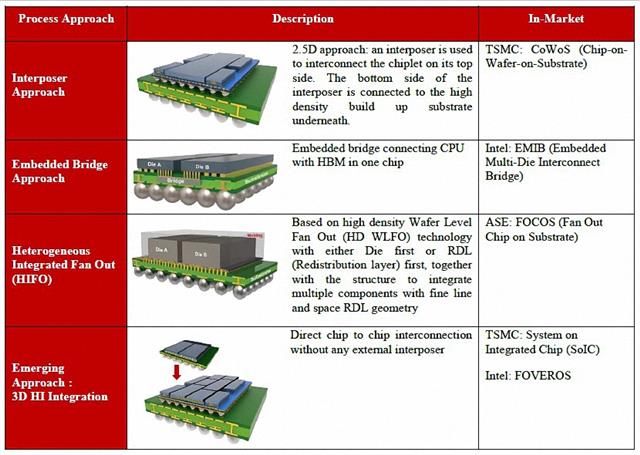

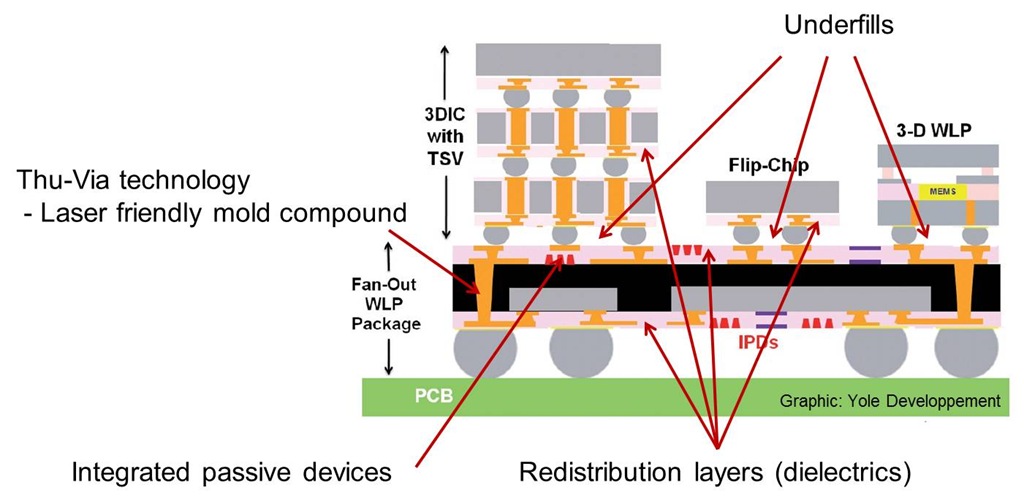

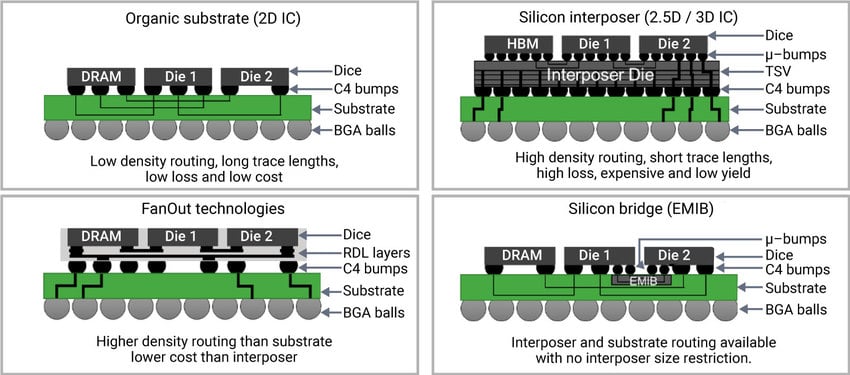

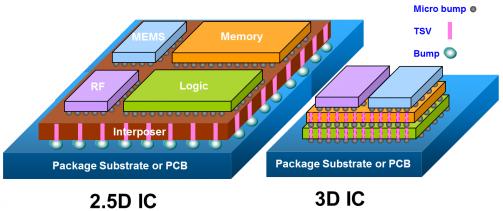

25/3D Level Heterogeneous Integration • Heterogeneous Integration • In the context of describing 25D/3D packaging level of technology • Integrating dissimilar chips using a packaging technology with I/O density higher than organic substrate (Feature size smaller than organic substrate, or 3D die) • Technology drivers • High bandwidth This integration scheme is called 25D TSV Additionally, silicon layers can be stacked tiertotier on top of each other, which reduces the physical area allocated for each component This tiertotier stacking is called 3D TSV technology In the dynamic random access memory (DRAM) space, 3D TSV has been deployed in both highbandwidth memory 2D vs 25D vs 3D ICs 101 By Max Maxfield 6 I see a lot of articles bouncing around the Internet these days about 25D and 3D ICs One really good one that came out recently was 25D ICs are more than a stepping stone to 3D ICs by Mike Santarini of Xilinx On the other hand, there are a lot of other articles that have "3D ICs

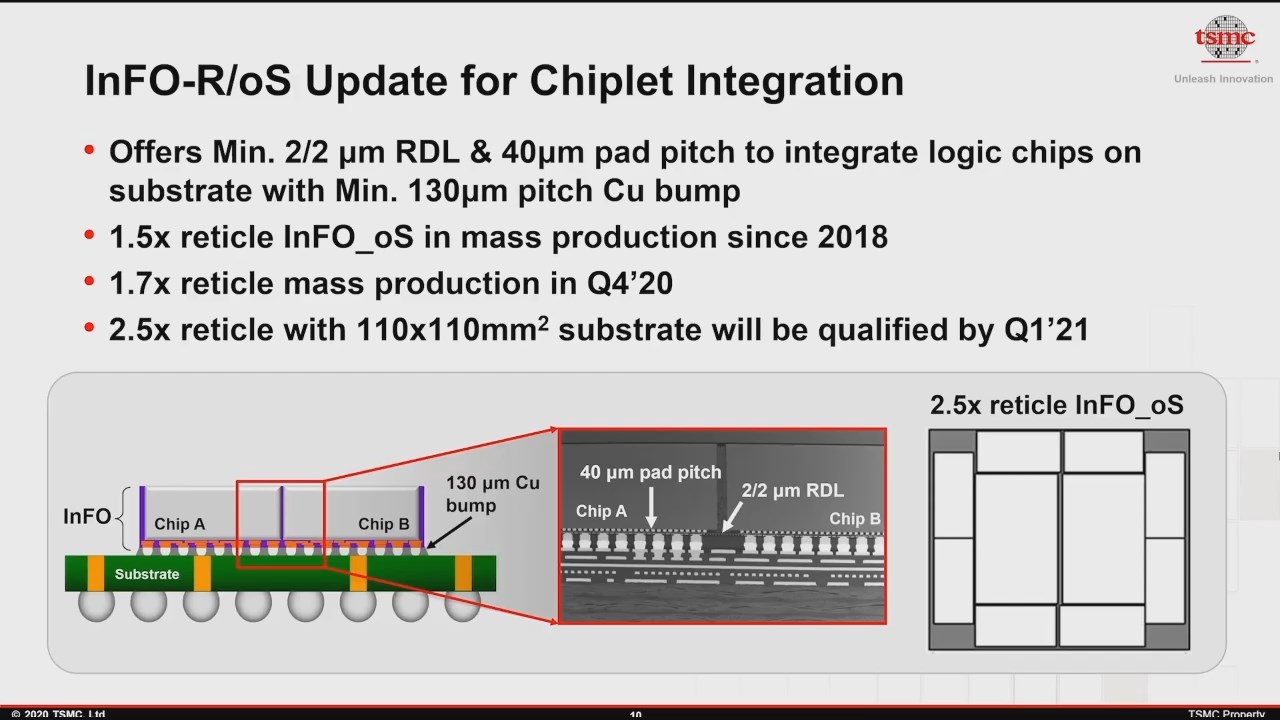

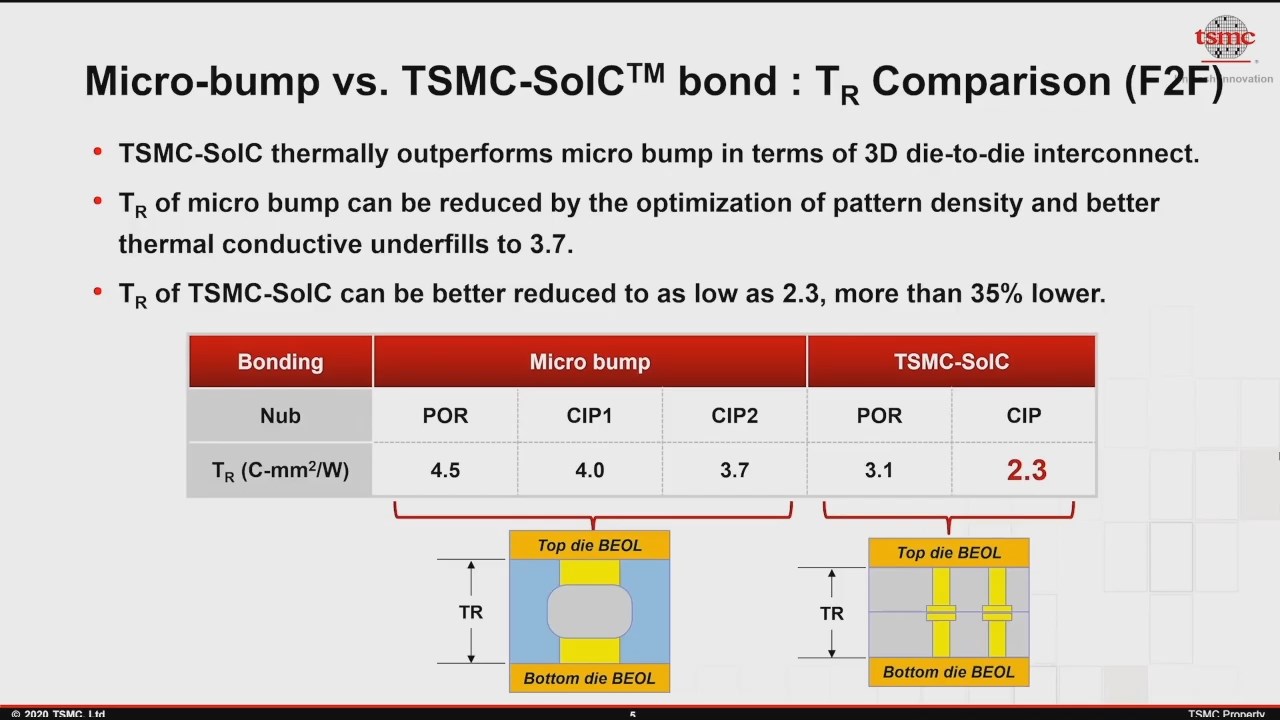

Iftle 381 Tsmc Wow Insights From Leading Edge

2.5 d vs 3d packaging

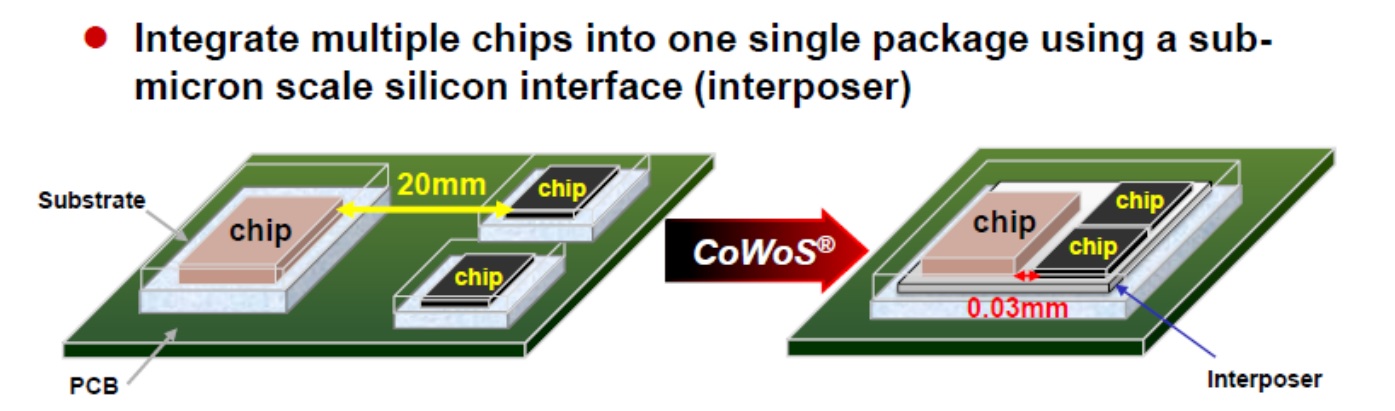

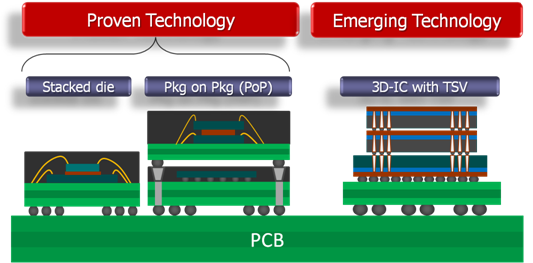

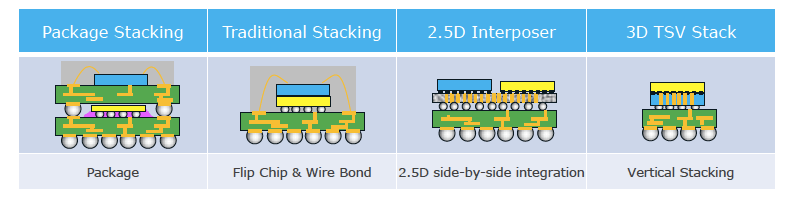

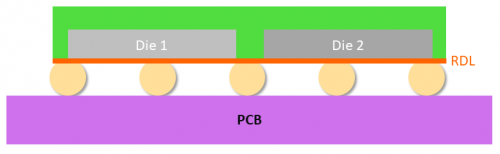

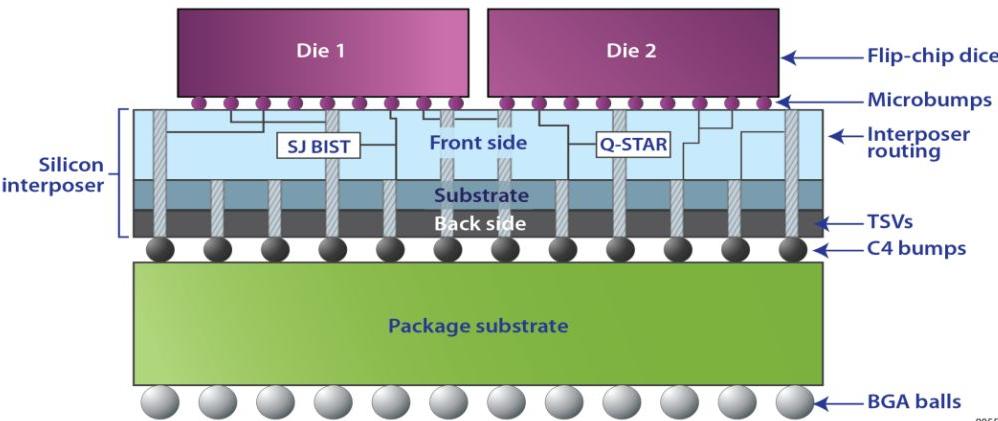

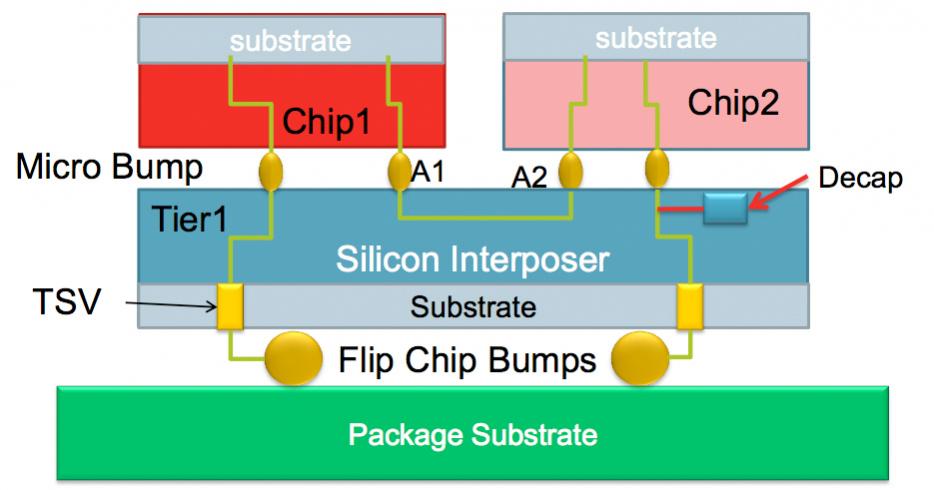

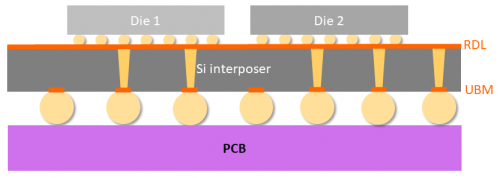

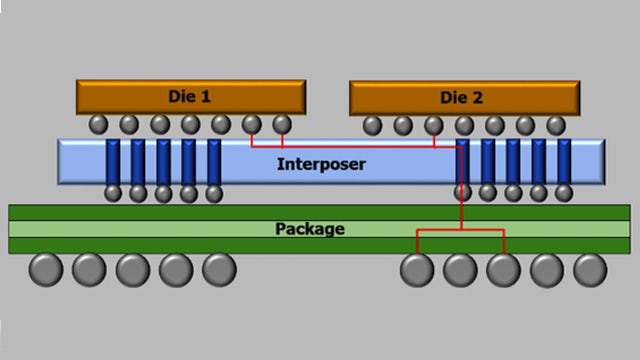

2.5 d vs 3d packaging- 3D and 25D packaging has been heralded as a set of the best package architectures to satisfy shrinking time to market windows while offering an effective way to combine the ever increasing set of circuits needed for today's popular products There is significant confusion as to the design guidelines and the economics involved to create a 3D 25D technology was first developed to be a bridge technology to 3D ICs, and has grown to be a package platform that is expected to coexist alongside 3D ICs Unlike in 3DICs, only the interposer, and not the dies themselves, needs TSVs to connect active die with package

2

Packaging Technologies GF Si nodes are qualified in a wide range of package technologies including 2D wirebond designs, flip chip, WLCSP and FOWLP configurations, as well as 25D, 3D and SiPhotonics The 25D package technologies leverage GF TSV Si interposer technology using 65nm and 32nm process node design rules,List of Tables 1 US 3d Ic And 25d Ic Market Size 18 2 Canada 3d Ic And 25d Ic Market Share 18 3 Brazil 3d Ic And 25d Ic Market Outlook 19 23 4 Mexico 3d Ic And 25d Ic Market Research 18 5 Germany 3d Ic And 25d Ic Market Trends 19 23 6 France 3d Ic And 25d Ic Market Growth 19 23GSA 3DIC Packaging July 14 ESystem Design Reference Design and Modeling for 3D ICs and Interposers, World Scientific Publishing Co Ltd Interconnect Technology Diameter (um) Oxide liner thickness (um) Length (um) Pitch (um) Material Properties R (m ) L (pH) G (mS) C (pF) Wirebond 25 1062 60 H r =43 tand=001 130 3 001 015 CGA/POP 40

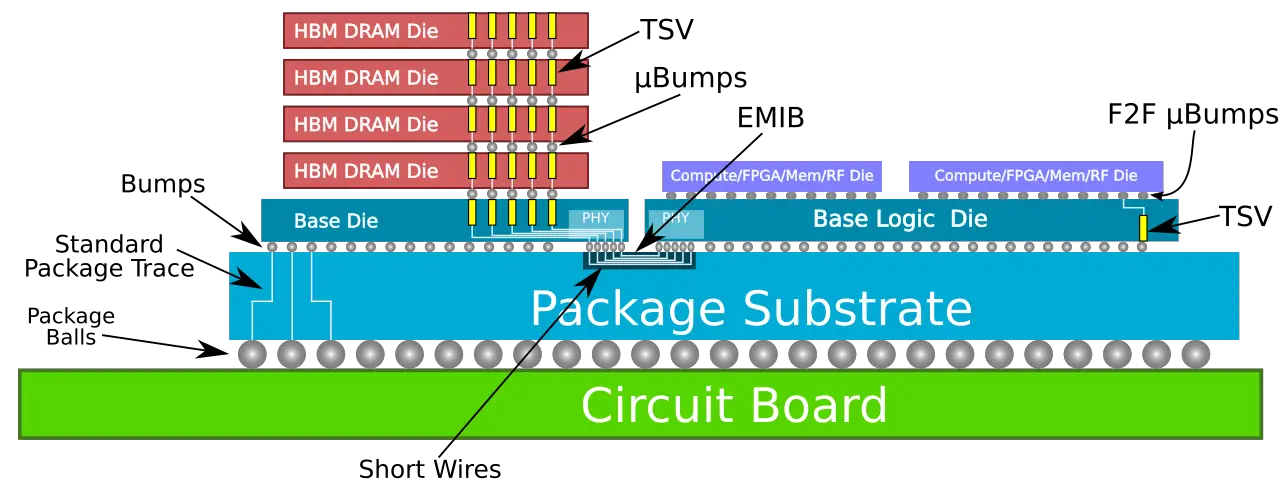

Through Silicon Via (TSV) interconnects have emerged to serve a wide range of 25D TSV and 3D TSV packaging applications and architectures that demand very high performance and functionality at the lowest energy/performance metric To enable the use of TSVs in 25D/3D TSV architectures, we have developed several backend technology platforms to In conclusion, 3D/25D packaging has now become an essential part of the semiconductor industry, extending Moore's Law at systemlevel The 3D/25D integration is accelerating 3D interconnect density (3D ID) into new highs Such is the value of 3D/25D packaging A strong adoption of endsystem units in cloud computing, networking, HPC, and He is involved in the market, technology and strategic analysis of the microelectronic assembly and packaging technologies His main interest areas are advanced IC packaging technology including equipment & materials He is the author of several reports on fanout / fanin WLP, flip chip, and 3D/25D packaging

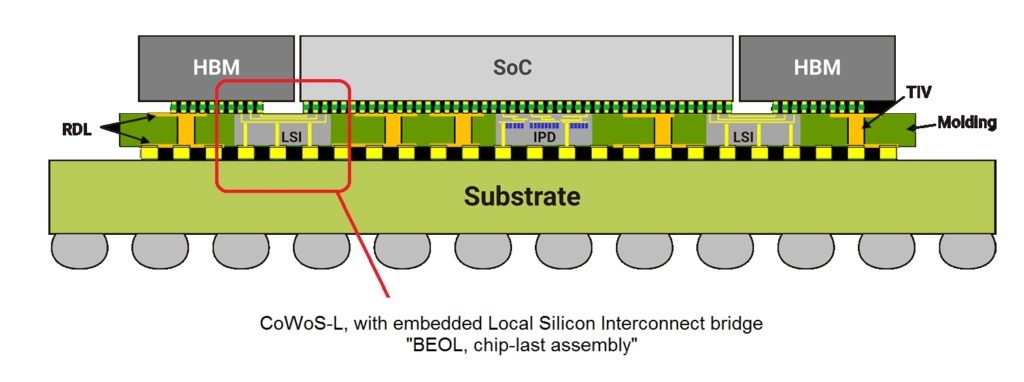

• This report is an update of the previous 17 release "3D TSV and 25D business update Market and Technology trends 17" • The scope of this report is to present the actual trends and their impact on the packaging need and especially the 25D/3D stacking technologiesTong expects commercialization of 25D chip technology to take place in two years Tong notes that 25D IC should notbe regarded as a transitional integration technology" Si Interposer "25D will enable packaging of chips in the 3222 nm nodes where the fragile mechanical stability of the lowK dielectrics used in these products will require Above Blending 25D and 3D packaging technologies yields CoEMIB, which enables largerthanreticle sized base dies plus Foveros die

Semicap Primer Packaging History And Primer By Mule Mule S Musings

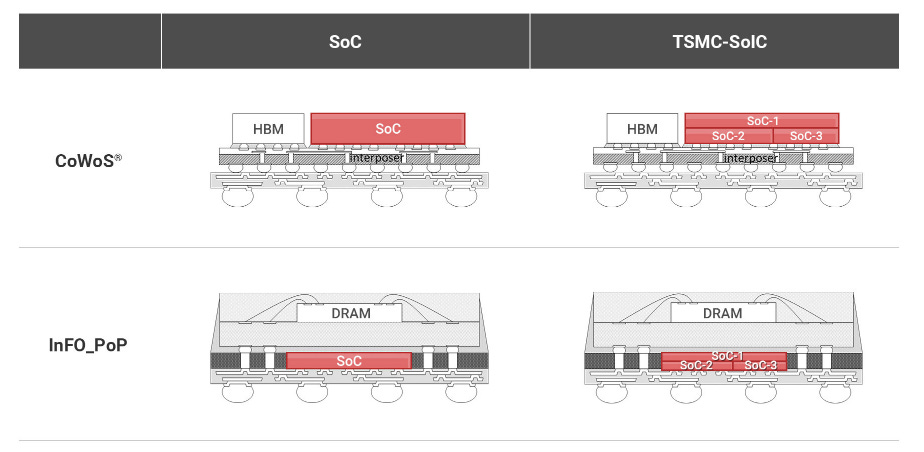

Chip On Wafer On Substrate Cowos Tsmc Wikichip

• 25/3D packaging process and materials are more sophisticated than in the traditional flip chip packaging technology o The industry mainstream SoA 25/3D package assembly process, materials, and business model are not currently compatible with low volume production for mil/space components25D is a packaging methodology for including multiple die inside the same package The approach typically has been used for applications where performance and low power are critical Communication between chips is accomplished using either a silicon or organic interposer, typically a chip or layer with throughsilicon vias for communicationMorethanMoore 25D and 3D SiP Integration Provides a detailed review of the stateoftheart in MorethanMoore technology options, including strengths and weaknesses of each This book presents a realistic and a holistic review of the microelectronic and semiconductor technology options in the post Moore's Law regime

Advanced Semiconductor Packaging Starting To Change Memory Market Landscape Seeking Alpha

Lost In The Advanced Ic Packaging Labyrinth Know These 10 Basic Terms Edn

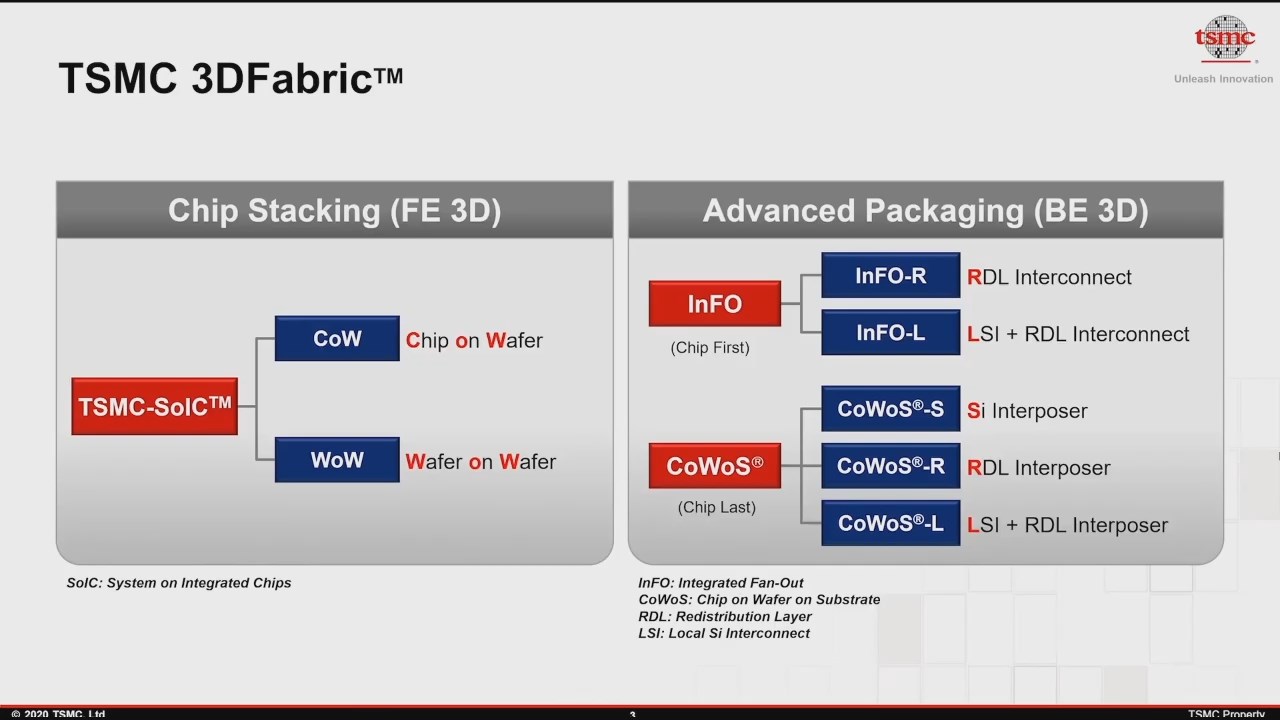

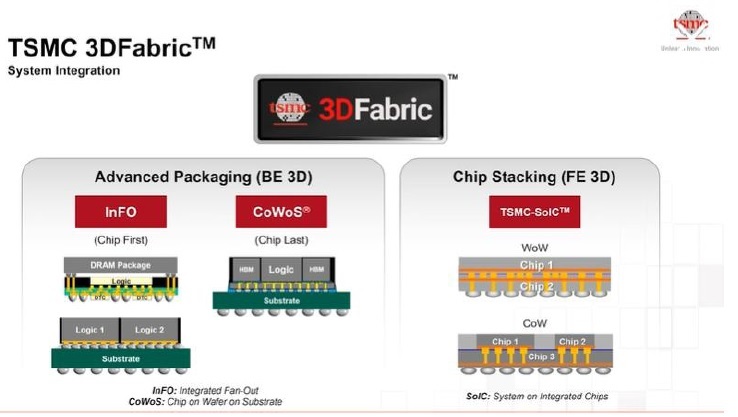

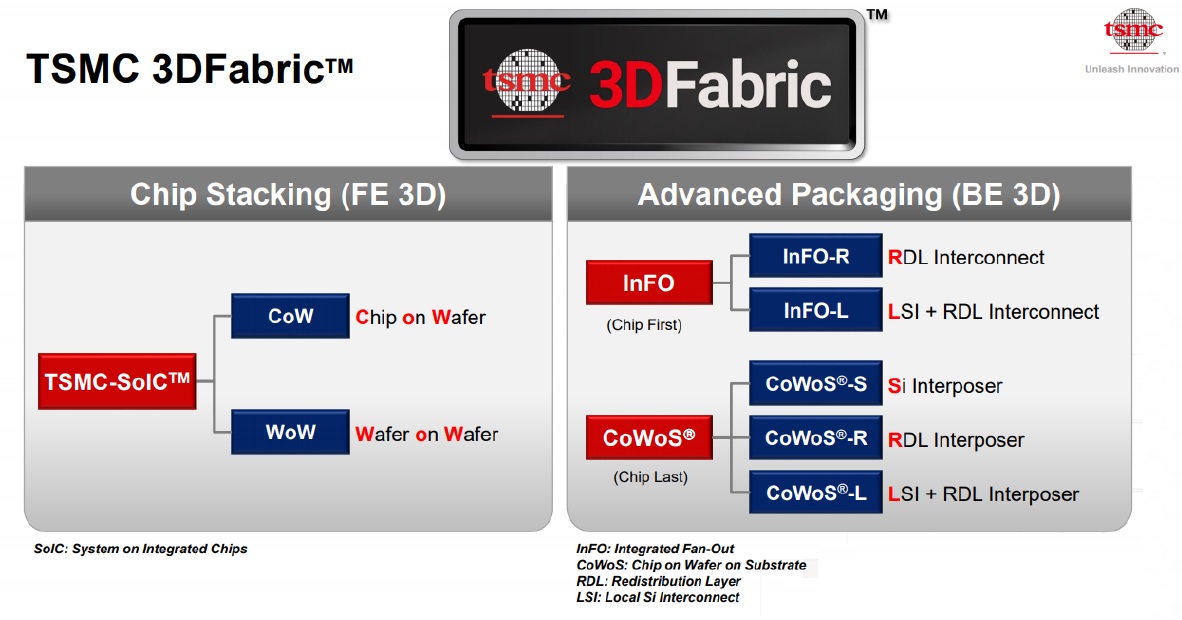

3DIC & 25D TSV INTERCONNECT FOR ADVANCED PACKAGING Intel Foveros Cross section and schematic view, Document 33 kB Last modifications Intel Foveros dissassembly & cross section Document 1016 kB Last modifications Highend packaging Roadmap Overall Risk, currently Lower 25D needs fewer new capabilities Need for standards Lower VerticalstackingMorecoordination 25D and 3D solutions can be combined in one IC package ! In order to unify all the different names it gives to its variants of its 25D and 3D packaging, TSMC has introduced its new overriding brand 3DFabric 3DFabric makes sense as a brand to tie the

Figure 1 From Wafer Warpage Experiments And Simulation For Fan Out Chip On Substrate Semantic Scholar

Solutions Bi Components Pte Ltd

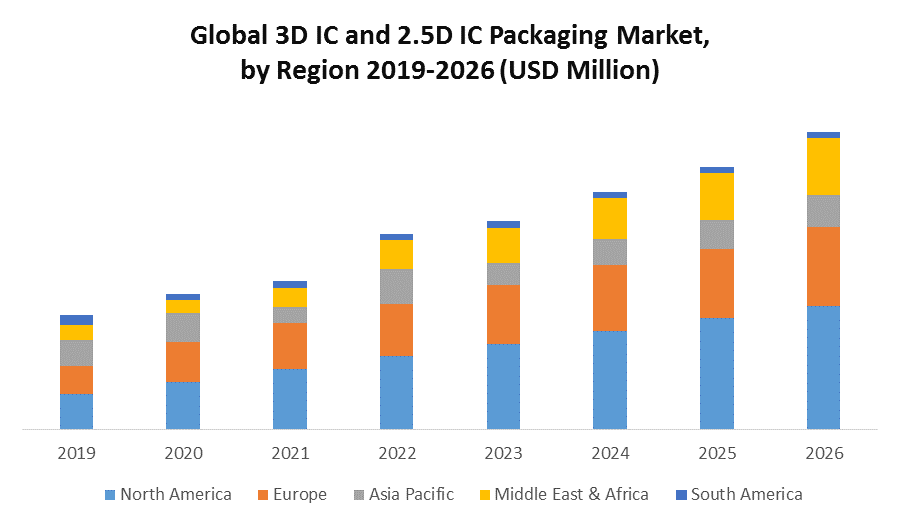

25D and 3D packaging are popular stereo packaging technology (Source ANSYS) The 25D packaging technology that is well known at present is nothing more than TSMC's CoWoS The concept of CoWoS technology is to put semiconductor chips (such as processors, memory, etc) together on the silicon intermediary layer, and then connect them to theThe major factors driving the 3D IC and 25D IC market for 3D TSV include highest interconnect density and greater space efficiencies in 3D TSV compared to all other types of advanced packaging, such as 3D WLCSP and 25 D Logic market accounted for the largest share of the 3D IC and 25D IC market in 15The market for 3D TSV and 25D interconnect is expected to reach around two million wafers in , expanding at a 22% compound annual growth rate (CAGR) The growth is driven by increased adoption of 3D memory devices in highend graphics, highperformance computing, networking and data centers, and penetration into new areas, including

Automated Latch Up Verification In 2 5d 3d Ics In Compliance Magazine

Different 3d Technologies Arranged According To Manufacturing Costs And Download Scientific Diagram

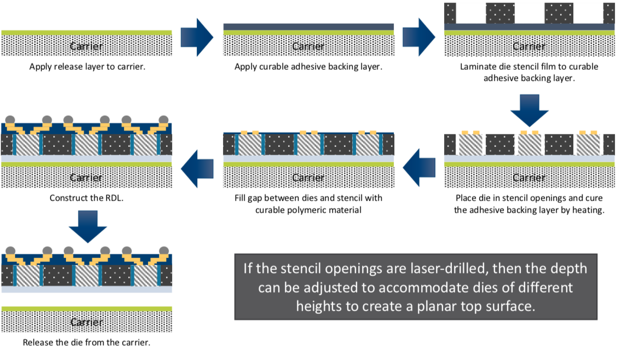

25D & 3D Packaging Indium Corporation is a world leader in the design, formulation, manufacture and supply of semiconductorgrade fluxes and associated materials, enabling 25 and 3D assembly processes, as well as more standard flipchip assembly Stencil technology has evolved throughout the years, and SysteminPackage solder pastes require Threedimensional (3D) packaging with throughsiliconvias (TSVs) is an emerging technology featuring smaller package size, higher interconnection density, and better performance; The Market Needs a New Kind of 3D Field Solver As shown in the figure below, the 25D and 3D parasitic extraction tools market currently consists of Finite element method (FEM)/boundary element method (BEM) tools (3D), which use numerical solvers to

3d Ic And 2 5d Ic Packaging Market In Depth Analysis Taiwan

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

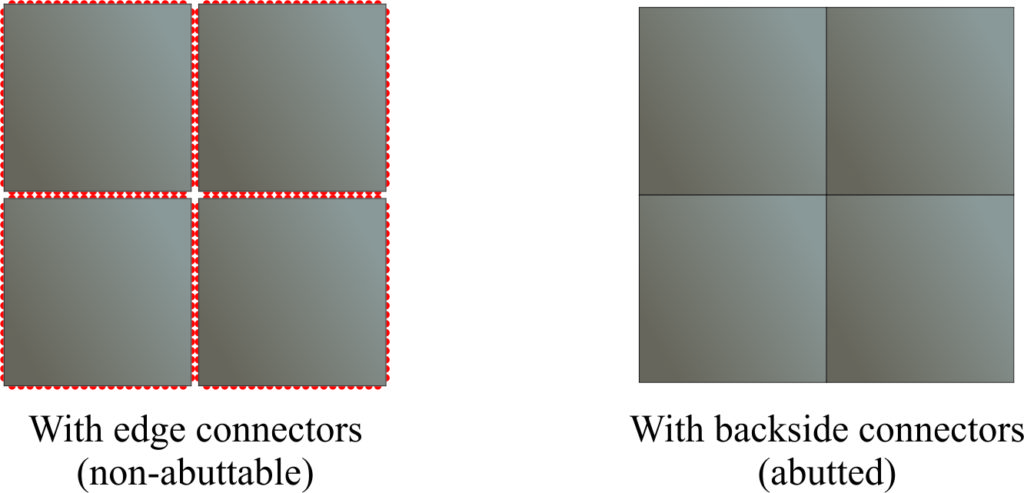

Coming 25D and 3D products pose new challenges to the production test environment Providing a commodity viable 3D product demands implementation of unique test and handling solutions Yield is the foremost concern but cost sensitivity and test economics are 25D vs Fanout Chip on Substrate WeiHong Lai 12/8/ Technology The demand for high bandwidth and highperformance applications such as networking, AI computing and GPU IC chips are driving innovative developments in advanced IC packaging Heterogeneous integration enables the integration of multiple chips using fine line/space The overall IC packaging market is projected to reach $68 billion in 19, up 35% over 18, according to Yole Développement Of those figures, advanced packaging is projected to grow at 43% in 19, compared to 28% for traditional/commodity packaging, according to Yole More 25D/3D and chiplets IC packaging is important for several reasons

Insights From Leading Edge Insights From Leading Edge Page 4

2 5d Chiplet Integration With An Interposer Download Scientific Diagram

25D packaging using silicon interposers with TSVs is an incremental step toward 3D packagingFraunhofer IZM's FOPLP), 3D IC packaging (TSMC's InFO_PoP vs Samsung's ePoP), 3D IC integration (Hynix/Samsung's HBM for AMD/NVIDIA's GPU vs Micron's HMC for Intel's Knights Landing CPU), 25D IC Integration (Xilinx/TSMC's CoWoS and TSVless interconnects and Glass vs Silicon Interposers for 25D and 3D IC Applications There has been enough interest stirred up in R&D around glass as a lowcost alternative interposer substrate material compared with silicon, that there was an entire session dedicated to developments in that area at the 12 IMAPS International Device Packaging conference, held

Glass Packaging R D For 2 5d Rf 5g Photonics Autonomous 17 05 01آ 18 Ieee Cpmt Workshop A Glass Pdf Document

2

However, substrate based IC packaging for 3D applications can adopt a wider range of materials and there are several alternativeIn this presentation we clarify one of the most confusing topics in xray inspection the difference between 2D, 25D, and 3D xray inspection Check the slides to see if you can tell if an image is 2D, 25D, or 3D!Chip Packaging Part 4 25D and 3D Packaging Dr Navid Asadi's group examines 25D and 3D packaging for expanding capabilities and capacities of chip solutions Peter Xi

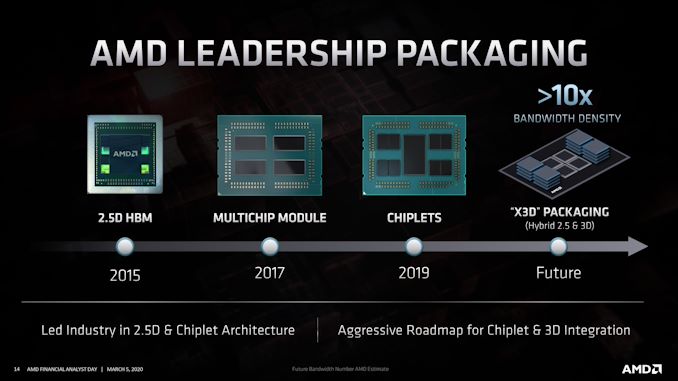

Amd Discusses X3d Die Stacking And Packaging For Future Products Hybrid 2 5d And 3d

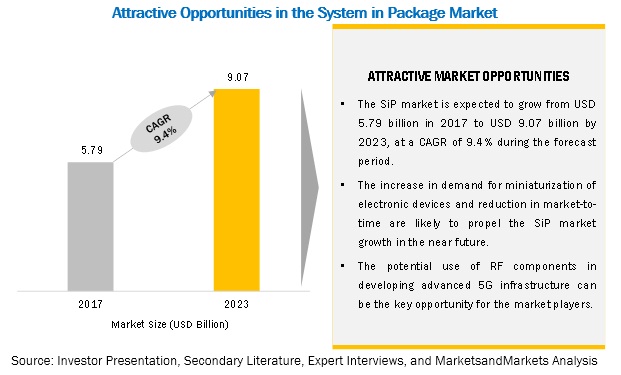

System In Package Market By Packaging Technology Package Packaging Method Device Application Covid 19 Impact Analysis Marketsandmarkets

(a) 2D (b) SI Design (c) 3D (d) 25D Figure 1 Various packaging options 23 Summarizing the Experiments and Motivation Behind Them A 3D system provides a large number of connections between the DRAM and the processor layer which can be used to increase the DRAM bandwidth However, the new challenge is to e ciently manage this bandwidth #2 In general, 3D packaging's processing feature sizes are huge (in microns vs in nanometers in actual leading edge logic devices) So ASML does not play a role in this space (or at least EUV is not needed, and will never be needed) Instead, lithography equipment handling bigger features but with higher productivity, like fromThe material presented will also reference 3D packaging standards and recognize innovative technologies from a number of industry sources, roadmaps and market forecasts Key words 25D, 3D Semiconductor Package Technology, Through Silicon Via, TSV, Through Glass Via, TGV

2 5d 3d Tsv Processes Development And Assembly Packaging Technology Semantic Scholar

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Together with 25D/3D packaging this extends Moore's Law at systemlevel" Without a doubt, times have changed, highend performance packaging is enabling systemlevel 25D/3D integration trendMultiple die packaging commonly utilizes some form of substrate interposer as a base Assembly of semiconductor die onto a substrate is essentially the same as those used for standard I/C packaging in lead frames;• The Advanced Packaging market was worth ~$2B in 19 It is expected to grow at ~ 7% CAGR 1925 to reach ~$422B in 25 • Highest revenue CAGR expected from 25D / 3D stacking IC, ED (in laminate substrate) and FanOut, 21%, 18% and 16%, respectively, as high volume products further penetrate the market FO in mobile,

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

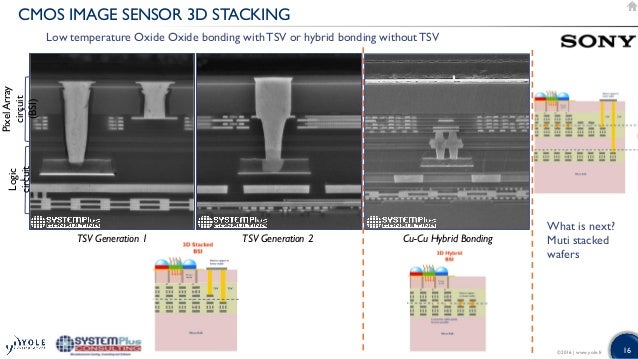

3D System on Chip * √ √ Silicon photonics √ √ √ √ 3D Stacked IC find their place in performance demanding applications * 3D System on Chip consists in logiconlogic and memoryonlogic stacked 3D ICA 25D integrated circuit (25D IC) combines multiple integrated circuit dies in a single package without stacking them into a threedimensional integrated circuit (3DIC) with throughsilicon vias (TSVs) The term "25D" originated when 3DICs withTo use new packaging strategies – 25D and 3D Moreover, these advanced packages enable highvalue logic chips at the current node to be combined with memory and lower density logic in a more economical manner than monolithic devices In turn, this is driving the development of thin (~

2

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

5221 Major Benefits of 25D Ic Packaging Over the Traditional 2D Packaging Practices 523 3D Ic Packaging Technology 524 2D Vs 25D Vs 3D Ic Packaging Technology 53 System in Package (SIP

Heterogeneous Integration Hi Ase Group

About 2 5d Technology Nhanced Semiconductors Inc

2

Semiconductor Packaging Inspection Teraview

Iftle 1 Imaps Device Packaging Conf Part 2 Amd Scp Insights From Leading Edge

2

Global 3d Ic And 2 5d Ic Packaging Market 17 Taiwan

Advanced Packaging Confusion Athisnews

2

3d Packaging 3d Incites

Highlights Of The Tsmc Technology Symposium Part 2 Semiwiki

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

Design Electrical Mechanical Thermal Prc Gatech Edu Georgia Institute Of Technology Atlanta Ga

More 2 5d 3d Fan Out Packages Ahead

3d Ic Emc Ppt Download

A Schematics Of The Three Integration Approaches 2d 3d And 2 5d Download Scientific Diagram

Iftle 454 Tsmc Exhibits Packaging Prowess At Virtual Ectc 3d Incites

3d Multi Chip Integration And Packaging Technology For Nand Flash Memories Springerlink

2 5d 3d Packaging Pradeep S Techpoints

2 5d Fo Wlp Issues Come Into Focus

Technology Challenges Ece Cs 752 Fall Ppt Download

Sensors In 3d And 2 5d Nhanced Semiconductors Inc

2 5d 3d Ic Market Challenges Opportunities

2

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Advanced Packaging Five Trends To Watch In 17 Electronic Products

2

The Evolution Of Heterogeneous Integration Enables The Coming Ai Era

Fan Out Chip On Substrate Ase Group

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Polymer Challenges In Electronic Packaging Overview Polymer Innovation Blog

Eetimes 3d Ic Design

Packaging Wars Begin

What S The Best Advanced Packaging Option Cyberoptics

3d Packaging A Key Enabler For Further Integration And Performance A

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Highlights Of The Tsmc Technology Symposium 21 Packaging Semiwiki

About 2 5d Technology Nhanced Semiconductors Inc

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

What S The Best Advanced Packaging Option Cyberoptics

Highlights Of The Tsmc Technology Symposium Part 2 Semiwiki

2 5d

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Wikichip Fuse

2 5d 3d Ase Group

Tsv Bist Die Level Integrity Monitors Ridgetop Group

Interposer Wikipedia

Advanced Packaging Strong Momentum Driven By Tsmc Intel And Samsung Ee Times Asia

3d Thursday 28nm Design And 2 5d Packaging Saves Xilinx A Ton Of Power You Can Too Even If You Re Not Designing Fpgas Eda360 Insider

Fan Out Chip On Substrate Ase Group

The Partially Molded 2 5d Packages And Assembly On The Board In Download Scientific Diagram

1

2 5d And 3d Designs Semiwiki

Production Test Of System In Package With Die To Die Phy Ip

Advanced Packaging Five Trends To Watch In 17 Electronic Products

3d And 2 5d Packaging Assembly With Highly Silica Filled One Step Chip Attach Materials For Both Thermal Compression Bonding And Mass Reflow Processes Semantic Scholar

1

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Heterogeneous Integration Hi Ase Group

2

3d And 2 5d Packaging Assembly With Highly Silica Filled One Step Chip Attach Materials For Both Thermal Compression Bonding And Mass Reflow Processes Semantic Scholar

1

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

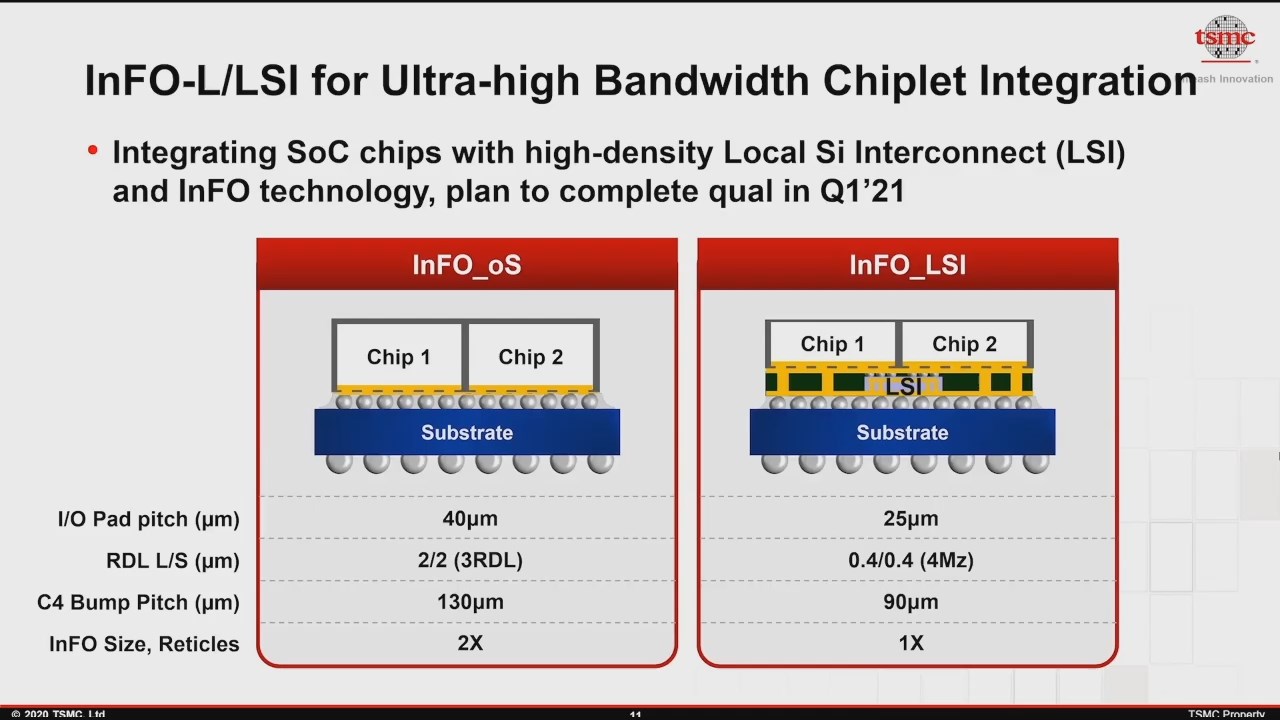

Tsmc S Version Of Emib Is Lsi Currently In Pre Qualification

3d Ic And 2 5 D Ic Packaging Industries In Depth Analysis

Global 3d Ic And 2 5d Ic Packaging Market Industry Analysis

2

Integrated Circuit Packaging And Gct The Samtec Blog

System In Package Ase Group

Semiconductor Foundry Support Siemens Digital Industries Software

Semiconductor Packaging 3d Ic Emerging As Innovation Enabler Semiwiki

2

Interconnect Research At Tsmc Page 1 Research Taiwan Semiconductor Manufacturing Company Tsmc English

Iftle 381 Tsmc Wow Insights From Leading Edge

3d 2 5d Ic Based Obfuscation Springerlink

Intel Leans Hard On Advanced Chip Packaging Technologies In Battle For Computing Supremacy Venturebeat

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Fan Out Wafer Level Packaging The Samtec Blog

Conventional Process Flow For 2 5d 3d Ic Integration Chip On Download Scientific Diagram

More 2 5d 3d Fan Out Packages Ahead I Micronews

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

0 件のコメント:

コメントを投稿